信息娛樂和儀表板通用的晶振分數分頻輸出

時鐘晶振是眾多電子產品所必備的電子元器件之一,應用領域廣泛,是看起來微小卻不可缺席的電子零件,石英晶振在不同的產品范圍使用不同的頻率頻段輸出,無源晶振通常使用在較低的頻率輸出領域,且信號較平穩,而有源晶振的頻率使用范圍通常較高,且信號傳輸快速,高質量,今天主要講述的是石英晶體振蕩器的分數輸出分頻PLL用于信息娛樂和儀表板應用的價值.

傳統上,石英晶體振蕩器(XO)用于在系統內生成每個時鐘,信息娛樂和儀表板系統通常需要幾個時鐘:處理器時鐘,PCIExpress時鐘,USB時鐘等-每個時鐘都以特定頻率為特征,在信息娛樂和儀表板應用所需的所有時鐘中,LCD面板點時鐘可能是最難實現的,目標點時鐘頻率由LCD面板的結構參數決定,例如分辨率,刷新率,有效/無效像素比等,雖然存在標準點時鐘頻率(例如27 MHz或148.5MHz),但某些LCD面板需要非標準頻率,我們以兩個隨機值為例,30.123MHz和40.456MHz,而這兩種頻段是很難能可貴的.

今天的設計可以依靠集成的可編程時鐘振蕩器,如汽車級VersaClock®6E5P49V60來解決這個問題,5P49V60可產生多達5種不同的頻率,最高可達350MHz,得益于分數輸出分頻器(FOD)PLL技術,該器件適用于生成我們示例的30.123MHz和40.456MHz,傳統PLL的分頻器只能有整數值,生成30.123和40.456MHz的示例頻率可以通過以下方式完成:(請注意,確實存在其他可能性).

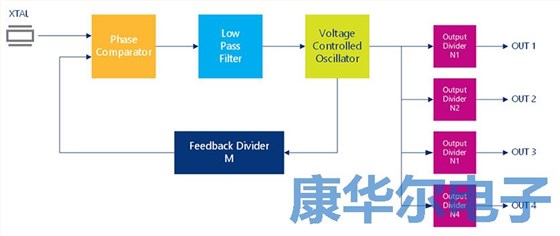

讓我們退后一步,詳細探討PLL(鎖相環)技術,PLL包括相位比較器,低通濾波器,壓控晶體振蕩器(VCO)以及反饋分頻器M和(在Versaclock6E的情況下)四個輸出分頻器N1,N2,N3和N4,PLL調節VCO頻率,使相位比較器的兩個輸入"看到"相同的頻率,如果來自晶體的信號(例如25MHz)連接到相位比較器的一個輸入端,并且VCO的輸出端除以系數M=100,則連接到相位比較器的另一個輸入端,PLL將針對fVCO=2500MHz的VCO頻率進行自我調整,VersaClock6E的合適VCO頻率范圍為2500MHz至2700MHz.

如我們所見,生成具有足夠低誤差的輸出頻率可能會很困難,此外,我們只考慮了整數輸出分頻器的局限性,如果我們想要根據可用的石英晶體頻率調整VCO頻率,則反饋分頻器M存在類似的限制,幸運的是,近年來分數輸出分頻器技術已經發展到可以實現具有"任何"N1,N2,N3,N4和M比率(在指定的設計范圍內)的點,通過將N1和N2設置為:可輕松生成30.123和40.456MHz的LCD點時鐘頻率:假設VCO頻率為2500MHz,在這種特殊情況下,5P49V60在f1上的誤差為0ppm,在f2上的誤差為0.5 ppb,(0.5ppb遠低于晶體諧振器的容差!)有時,VCO頻率可能會影響器件的性能.

高度集成低功率射頻和混合信號系統芯片結合石英晶振服務于眾多市場領域,包括智能照明,家庭自動化,智能城市和其他消費電子市場,其開發現有的傳感器技術保持更好的更好的功率平衡性能,在物聯網產品連接領域中占據了領銜優勢,晶振在如今眾多優質的電子元器件激烈的競爭中發揮自身獨特的產品性能,在電子零件領域擁有屬于自己的產品市場.

進口愛普生晶振FA-20H,Q24FA20H00005水晶振動子

進口愛普生晶振FA-20H,Q24FA20H00005水晶振動子 EPSON愛普生晶振C-2,Q12C20001000600水晶振動子

EPSON愛普生晶振C-2,Q12C20001000600水晶振動子 SMD-49無源諧振器,KDS日本晶體,1AJ250004B兩腳無源晶振

SMD-49無源諧振器,KDS日本晶體,1AJ250004B兩腳無源晶振